X11DPH-I X11DPH-T X11DPH-TQ

**USER'S MANUAL**

Revision 1.0b

The information in this User's Manual has been carefully reviewed and is believed to be accurate. The vendor assumes no responsibility for any inaccuracies that may be contained in this document, and makes no commitment to update or to keep current the information in this manual, or to notify any person or organization of the updates. **Please Note:** For the most up-to-date version of this manual, please see our website at www.supermicro.com.

Super Micro Computer, Inc. ("Supermicro") reserves the right to make changes to the product described in this manual at any time and without notice. This product, including software and documentation, is the property of Supermicro and/ or its licensors, and is supplied only under a license. Any use or reproduction of this product is not allowed, except as expressly permitted by the terms of said license.

IN NO EVENT WILL Super Micro Computer, Inc. BE LIABLE FOR DIRECT, INDIRECT, SPECIAL, INCIDENTAL, SPECULATIVE OR CONSEQUENTIAL DAMAGES ARISING FROM THE USE OR INABILITY TO USE THIS PRODUCT OR DOCUMENTATION, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. IN PARTICULAR, SUPER MICRO COMPUTER, INC. SHALL NOT HAVE LIABILITY FOR ANY HARDWARE, SOFTWARE, OR DATA STORED OR USED WITH THE PRODUCT, INCLUDING THE COSTS OF REPAIRING, REPLACING, INTEGRATING, INSTALLING OR RECOVERING SUCH HARDWARE, SOFTWARE, OR DATA.

Any disputes arising between manufacturer and customer shall be governed by the laws of Santa Clara County in the State of California, USA. The State of California, County of Santa Clara shall be the exclusive venue for the resolution of any such disputes. Supermicro's total liability for all claims will not exceed the price paid for the hardware product.

FCC Statement: This equipment has been tested and found to comply with the limits for a Class A digital device pursuant to Part 15 of the FCC Rules. These limits are designed to provide reasonable protection against harmful interference when the equipment is operated in a commercial environment. This equipment generates, uses, and can radiate radio frequency energy and, if not installed and used in accordance with the manufacturer's instruction manual, may cause harmful interference with radio communications. Operation of this equipment in a residential area is likely to cause harmful interference, in which case you will be required to correct the interference at your own expense.

<u>California Best Management Practices Regulations for Perchlorate Materials</u>: This Perchlorate warning applies only to products containing CR (Manganese Dioxide) Lithium coin cells. "Perchlorate Material-special handling may apply. See <a href="https://www.dtsc.ca.gov/hazardouswaste/perchlorate">www.dtsc.ca.gov/hazardouswaste/perchlorate</a>".

<u>WARNING</u>: Handling of lead solder materials used in this product may expose you to lead, a chemical known to the State of California to cause birth defects and other reproductive harm.

The products sold by Supermicro are not intended for and will not be used in life support systems, medical equipment, nuclear facilities or systems, aircraft, aircraft devices, aircraft/emergency communication devices or other critical systems whose failure to perform be reasonably expected to result in significant injury or loss of life or catastrophic property damage. Accordingly, Supermicro disclaims any and all liability, and should buyer use or sell such products for use in such ultra-hazardous applications, it does so entirely at its own risk. Furthermore, buyer agrees to fully indemnify, defend and hold Supermicro harmless for and against any and all claims, demands, actions, litigation, and proceedings of any kind arising out of or related to such ultra-hazardous use or sale.

Manual Revision 1.0b

Release Date: Oct. 31, 2017

Unless you request and receive written permission from Super Micro Computer, Inc., you may not copy any part of this document. Information in this document is subject to change without notice. Other products and companies referred to herein are trademarks or registered trademarks of their respective companies or mark holders.

Copyright © 2017 by Super Micro Computer, Inc. All rights reserved.

Printed in the United States of America

## **Preface**

## **About This Manual**

This manual is written for system integrators, IT technicians, and knowledgeable end users. It provides information for the installation and use of the X11DPH-i/T(q) motherboard.

## **About This Motherboard**

The Super X11DPH-i/X11DPH-T/X11DPH-Tq motherboard supports dual Intel® Xeon 81xx/61xx/51xx/41xx/31xx Series processors (Socket P) with the TDP (Thermal Design Power) of up to 205W and UPI (UltaPath Interconnect) of up to 10.4 GT/s. With the Intel C622/C624/C628 PCH built-in (Note below), this motherboard supports three PCI-E 3.0 x16 slots, four PCI-E 3.0 x8 slots, two PCI-E 3.0 x4 M.2 slots, ten SATA3 ports, seven USB 3.0 connections, and up to 2TB of LRDIMM/RDIMM/NVDIMM DDR4 ECC 2666/2400/2133 MHz memory in 16 memory slots. The X11DPH-i/T(q) provides maximum system performance, system cooling, and I/O expansion capability currently available on the market. This motherboard is optimized for general-purpose, high-performance computing, and is ideal for use as a storage server. Please note that this motherboard is intended to be installed and serviced by professional technicians only. For processor/memory updates, please refer to our website at http://www.supermicro.com/products/.

Notes: 1. Intel C622 is used for X11DPH-i, C624: is for X11DPH-T, and C628: for X11DPT-Tq. 2. The X11DPH-Tq supports Intel® QuickAssist Technology.

# Manual organization

**Chapter 1** describes the features, specifications and performance of the motherboard, and provides detailed information on the Intel C622/C624/C628 chipset.

**Chapter 2** provides hardware installation instructions. Read this chapter when installing the processor, memory modules and other hardware components into the system.

If you encounter any problems, see **Chapter 3**, which describes troubleshooting procedures for video, memory and system setup stored in the CMOS.

**Chapter 4** includes an introduction to the BIOS, and provides detailed information on running the CMOS Setup utility.

Appendix A provides BIOS Error Beep Codes.

**Appendix B** lists software program installation instructions.

**Appendix C** lists standardized warning statements in various languages.

**Appendix D** contains UEFI BIOS Recovery instructions.

# **Contacting Supermicro**

## Headquarters

Address: Super Micro Computer, Inc.

980 Rock Ave.

San Jose, CA 95131 U.S.A.

Tel: +1 (408) 503-8000 Fax: +1 (408) 503-8008

Email: marketing@supermicro.com (General Information)

support@supermicro.com (Technical Support)

Website: www.supermicro.com

**Europe**

Address: Super Micro Computer B.V.

Het Sterrenbeeld 28, 5215 ML

's-Hertogenbosch, The Netherlands

Tel: +31 (0) 73-6400390 Fax: +31 (0) 73-6416525

Email: sales@supermicro.nl (General Information)

support@supermicro.nl (Technical Support)

rma@supermicro.nl (Customer Support)

Website: www.supermicro.nl

**Asia-Pacific**

Address: Super Micro Computer, Inc.

3F, No. 150, Jian 1st Rd.

Zhonghe Dist., New Taipei City 235

Taiwan (R.O.C)

Tel: +886-(2) 8226-3990 Fax: +886-(2) 8226-3992

Email: support@supermicro.com.tw

Website: www.supermicro.com.tw

# **Table of Contents**

# Chapter 1 Introduction

| 1.1 | Checklist                                                                                                                | 9  |

|-----|--------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Processor and Chipset Overview                                                                                           | 19 |

| 1.3 | Special Features                                                                                                         | 20 |

| 1.4 | System Health Monitoring                                                                                                 | 20 |

| 1.5 | ACPI Features                                                                                                            | 21 |

| 1.6 | Power Supply                                                                                                             | 21 |

| 1.7 | Super I/O                                                                                                                | 21 |

| 1.8 | Advanced Power Management                                                                                                | 22 |

|     | Intel® Intelligent Power Node Manager (IPNM)                                                                             | 22 |

|     | Management Engine (ME)                                                                                                   | 22 |

| 1.9 | Intel® QuickAssist Technology (For the X11DPH-Tq only)                                                                   | 22 |

| Ch  | apter 2 Installation                                                                                                     |    |

| 2.1 | Static-Sensitive Devices                                                                                                 | 23 |

| 2.2 | Motherboard Installation                                                                                                 | 24 |

| 2.3 | Processor and Heatsink Installation                                                                                      | 26 |

|     | The Intel 81xx/61xx/51xx/41xx/31xx Series Processors                                                                     | 26 |

|     | Overview of the Processor Socket Assembly                                                                                | 27 |

|     | Overview of the Processor Heatsink Module (PHM)                                                                          | 28 |

|     | Attaching the Non-F Model Processor to the Narrow Processor Clip to Create the Processor Package Assembly                | 29 |

|     | Attaching the F Model Processor to the Narrow Processor Clip to Create the Process Package Assembly                      |    |

|     | Attaching the Non-F Model Processor Package Assembly to the Heatsink to Form the Processor Heatsink Module (PHM)         |    |

|     | Attaching the F Model Processor Package Assembly to the Heatsink to Form the Processor Heatsink Module (PHM)             | 32 |

|     | Preparing the CPU Socket for Installation                                                                                | 33 |

|     | Removing the Dust Cover from the CPU Socket                                                                              | 33 |

|     | Installing the Processor Heatsink Module (PHM)                                                                           | 34 |

|     | Installing an HFI Carrier Card for Host Fabric Interface (HFI) Support as Needed (Available when an F Model CPU is Used) | 35 |

|     | Removing the Processor Heatsink Module (PHM) from the Motherboard                  | 36   |

|-----|------------------------------------------------------------------------------------|------|

| 2.4 | Memory Support and Installation                                                    | 37   |

|     | Memory Support                                                                     | 37   |

|     | DIMM Population Requirements for the 81xx/61xx/51xx/41xx/31xx Series Processors    | 38   |

|     | DIMM Installation                                                                  | 41   |

|     | DIMM Removal                                                                       | 41   |

| 2.5 | Rear I/O Ports                                                                     | 42   |

| 2.6 | Front Control Panel                                                                | 47   |

| 2.7 | Connectors                                                                         | 52   |

|     | Power Connector                                                                    | 52   |

|     | Headers                                                                            | 54   |

|     | Host Fabric Interface (HFI) Carrier Card Sideband Header (for the F Model CPU Only | /)55 |

| 2.8 | Jumper Settings                                                                    | 63   |

|     | How Jumpers Work                                                                   | 63   |

| 2.9 | LED Indicators                                                                     | 68   |

| Ch  | apter 3 Troubleshooting                                                            |      |

| 3.1 | Troubleshooting Procedures                                                         | 70   |

| 3.2 | Technical Support Procedures                                                       | 74   |

| 3.3 | Frequently Asked Questions                                                         | 75   |

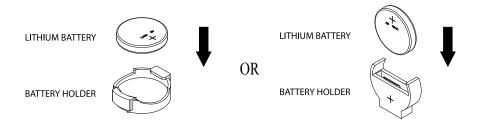

| 3.4 | Battery Removal and Installation                                                   | 76   |

|     | Battery Removal                                                                    | 76   |

|     | Proper Battery Disposal                                                            | 76   |

|     | Battery Installation                                                               | 76   |

| 3.5 | Returning Merchandise for Service                                                  | 77   |

| Ch  | apter 4 BIOS                                                                       |      |

| 4.1 | Introduction                                                                       | 78   |

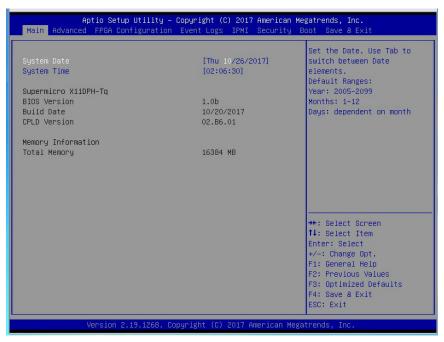

| 4.2 | Main Setup                                                                         | 79   |

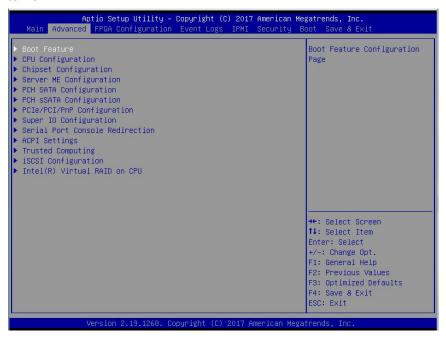

| 4.3 | Advanced Setup Configurations                                                      | 81   |

| 4.4 | Event Logs                                                                         | 109  |

| 4.5 | IPMI                                                                               | 111  |

| 4.6 | Security Settings                                                                  | 114  |

| 4.7 | Boot Settings                                                                      | 117  |

| 4.8 | Save & Exit                                                                        | 120  |

| Appendix A BIOS Codes                      |     |

|--------------------------------------------|-----|

| Appendix B Software Installation           |     |

| B.1 Installing Software Programs           | 124 |

| B.2 SuperDoctor® 5                         | 125 |

| Appendix C Standardized Warning Statements |     |

| Battery Handling                           | 126 |

| Product Disposal                           | 128 |

| Appendix D UEFI BIOS Recovery              |     |

# **Chapter 1**

## Introduction

Congratulations on purchasing your computer motherboard from an industry leader. Supermicro motherboards are designed to provide you with the highest standards in quality and performance.

In addition to the motherboard, several important parts that are included with your shipment are listed below. If anything listed is damaged or missing, please contact your retailer.

## 1.1 Checklist

| Main Parts List                 |                  |          |  |  |  |

|---------------------------------|------------------|----------|--|--|--|

| Description                     | Part Number      | Quantity |  |  |  |

| Supermicro motherboard-X11DPH-i | MNL-             | 1        |  |  |  |

| SATA cables                     | CBL-0044L (x2)   | 2        |  |  |  |

| I/O Backplane                   | MCP-260-00042-ON | 1        |  |  |  |

|                                 |                  |          |  |  |  |

|                                 |                  |          |  |  |  |

|                                 |                  |          |  |  |  |

|                                 |                  |          |  |  |  |

|                                 |                  |          |  |  |  |

|                                 |                  |          |  |  |  |

## **Important Links**

For your system to work properly, please follow the links below to download all necessary drivers/utilities and the user's manual for your server.

- Supermicro product manuals: http://www.supermicro.com/support/manuals/

- Product drivers and utilities: ftp://ftp.supermicro.com

- Product safety info: http://www.supermicro.com/about/policies/safety\_information.cfm

- If you have any questions, please contact our support team at: support@supermicro.com

This manual may be periodically updated without notice. Please check the Supermicro website for possible updates to the manual revision level.

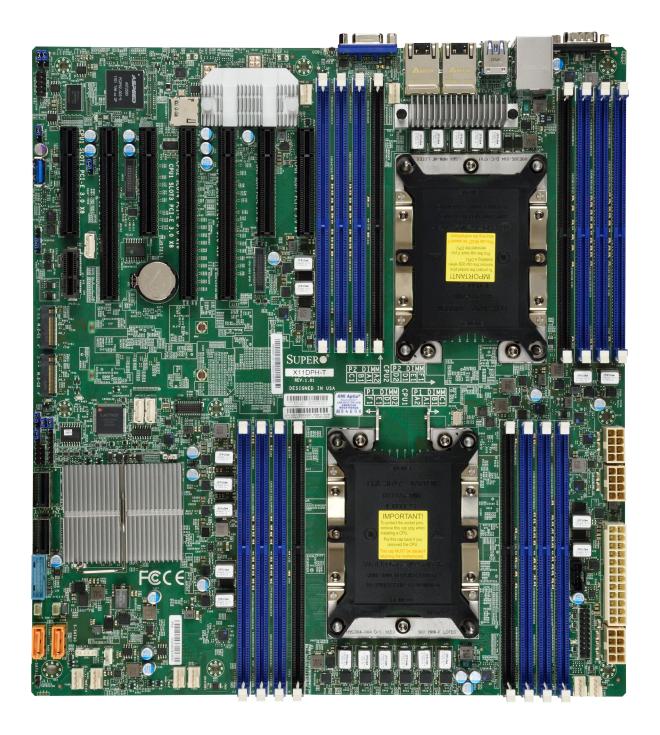

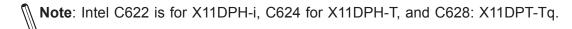

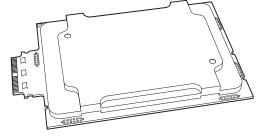

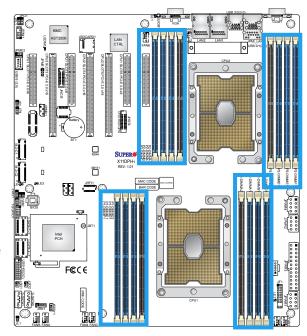

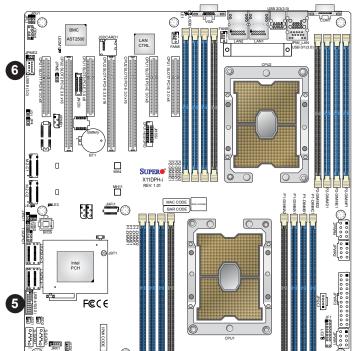

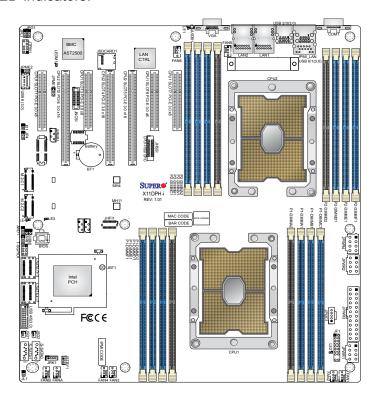

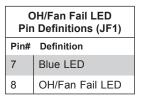

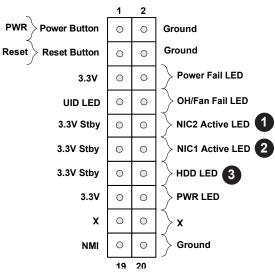

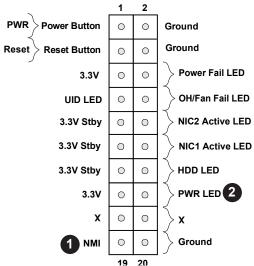

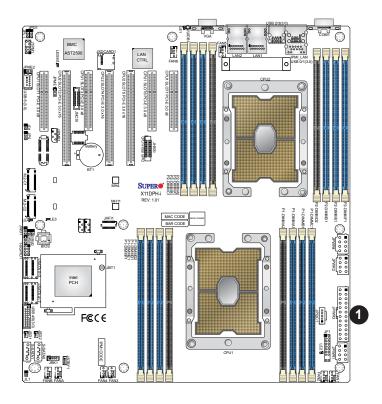

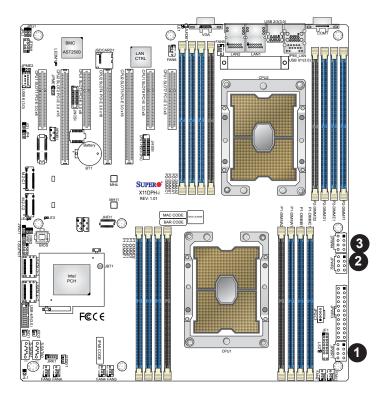

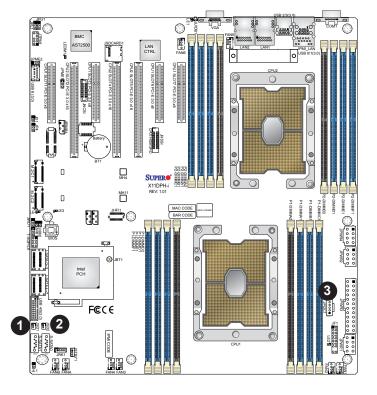

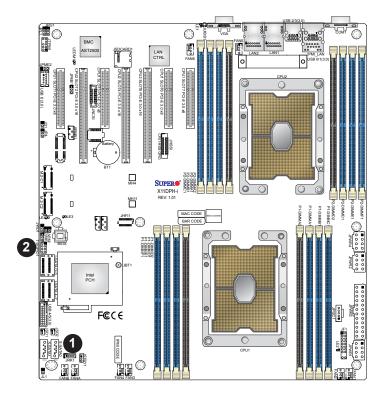

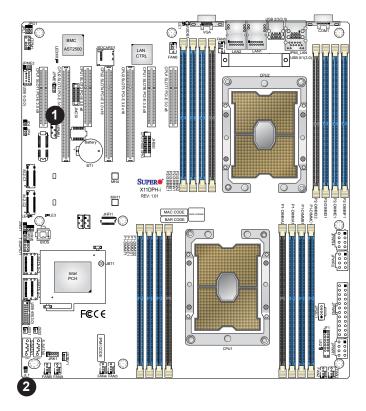

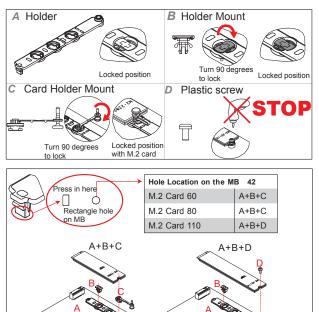

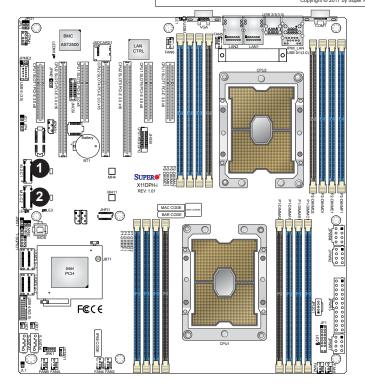

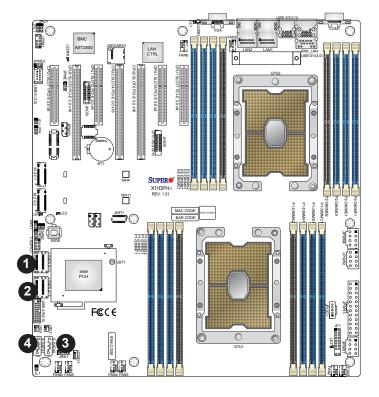

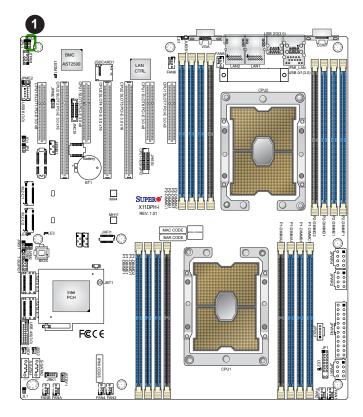

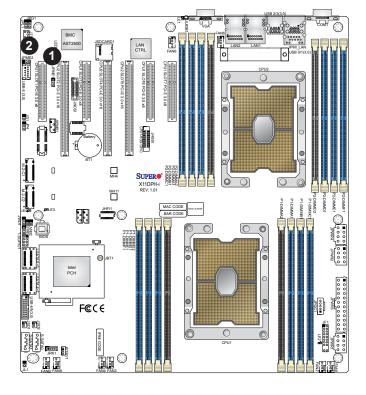

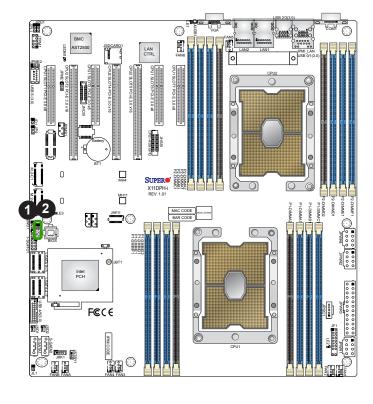

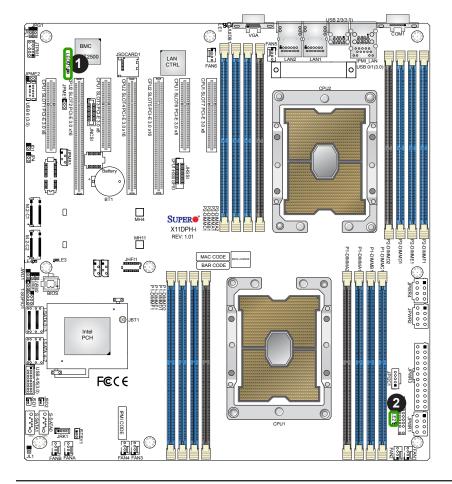

Figure 1-1. X11DPH-i/T(q) Motherboard Image

**Note:** All graphics shown in this manual were based upon the latest PCB revision available at the time of publication of the manual. The motherboard you received may or may not look exactly the same as the graphics shown in this manual.

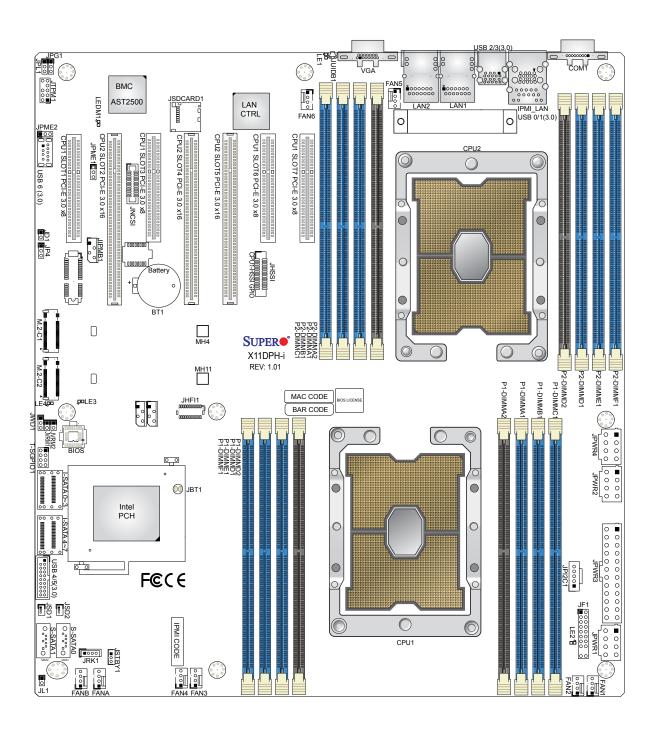

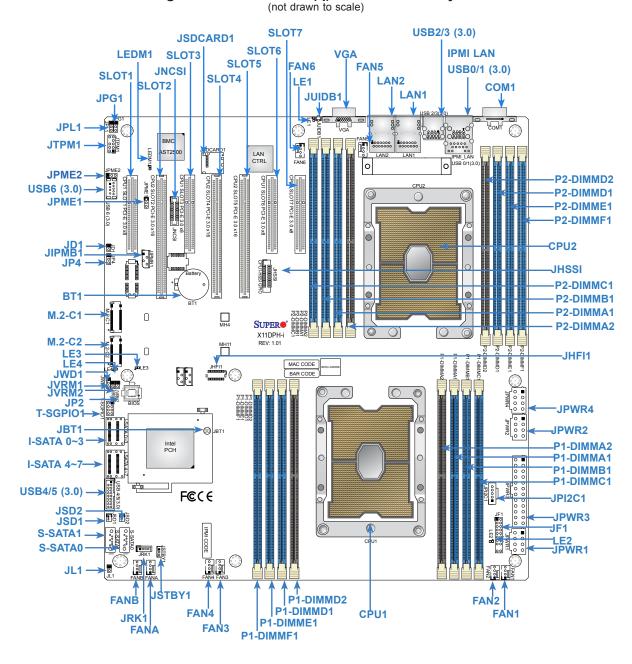

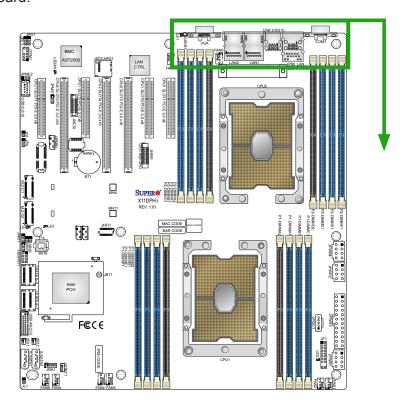

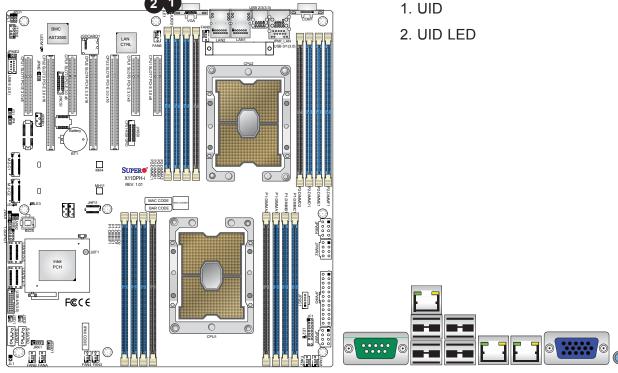

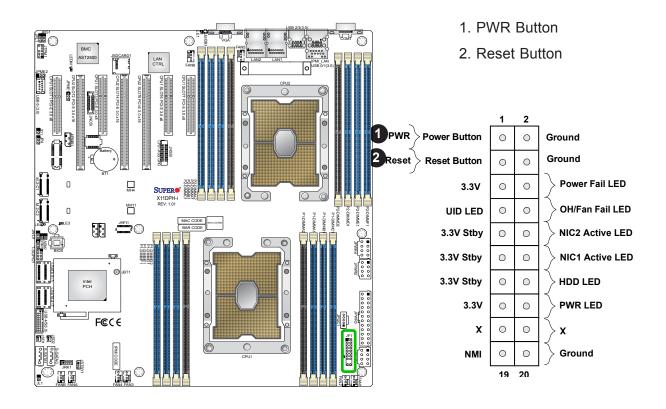

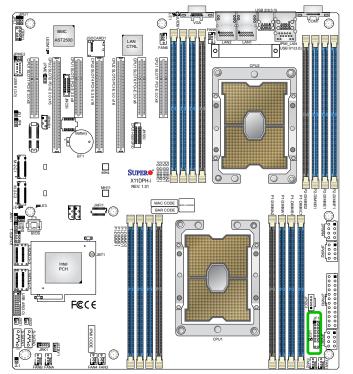

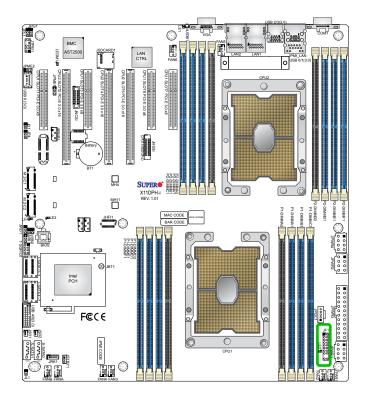

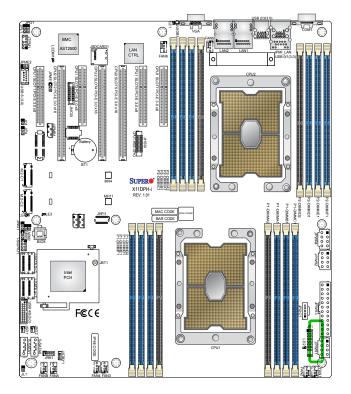

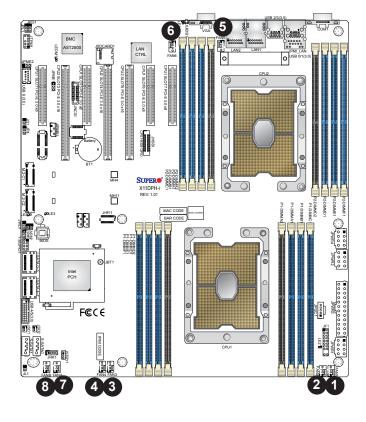

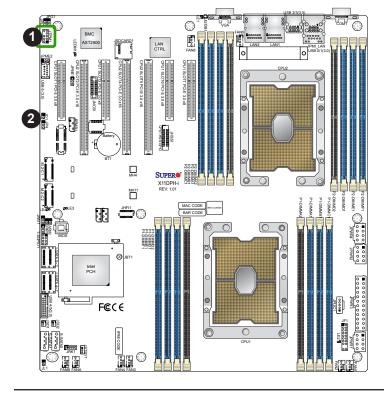

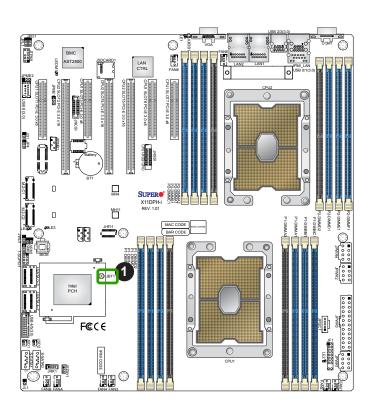

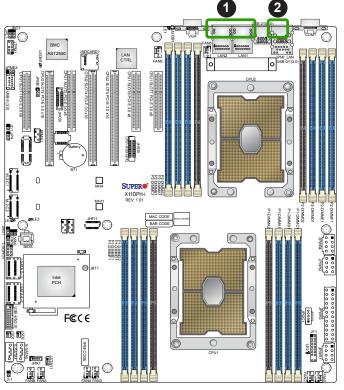

Figure 1-2. X11DPH-i/T(q) Motherboard Layout

#### Notes:

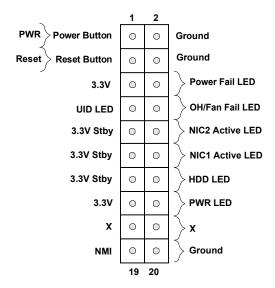

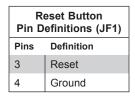

- See Chapter 2 for detailed information on jumpers, I/O ports, and JF1 front panel connections.

- "\( \) indicates the location of Pin 1.

- Jumpers/LED indicators not documented in this user manual are reserved for internal testing only.

- Use only the correct type of onboard CMOS battery as specified by the manufacturer. Do not install the onboard battery upside down to avoid possible explosion.

# **Quick Reference Table**

| Jumper                                                           | Description                                                 | Default Setting               |  |  |

|------------------------------------------------------------------|-------------------------------------------------------------|-------------------------------|--|--|

| JBT1                                                             | CMOS Clear Open (Normal)                                    |                               |  |  |

| JPG1                                                             | VGA Enable Pins 1-2 (Enabled)                               |                               |  |  |

| JPL1                                                             | LAN1/LAN2 Enable                                            | Pins 1-2 (Enabled)            |  |  |

| JPME1                                                            | ME Recovery                                                 | Pins 1-2 (Normal)             |  |  |

| JPME2                                                            | ME Manufacturing Mode                                       | Pins 1-2 (Normal)             |  |  |

| JVRM1                                                            | VRM SMB Clock (to BMC or PCH)                               | On (Normal: SMB Clock to BMC) |  |  |

| JVRM2                                                            | VRM SMB Data (to BMC or PCH)                                | On (Normal: SMB Clock to BMC) |  |  |

| JWD1                                                             | Watch Dog Timer Enable                                      | Pins 1-2 (Reset)              |  |  |

| Connector                                                        | Description                                                 |                               |  |  |

| BT1                                                              | Onboard CMOS battery                                        |                               |  |  |

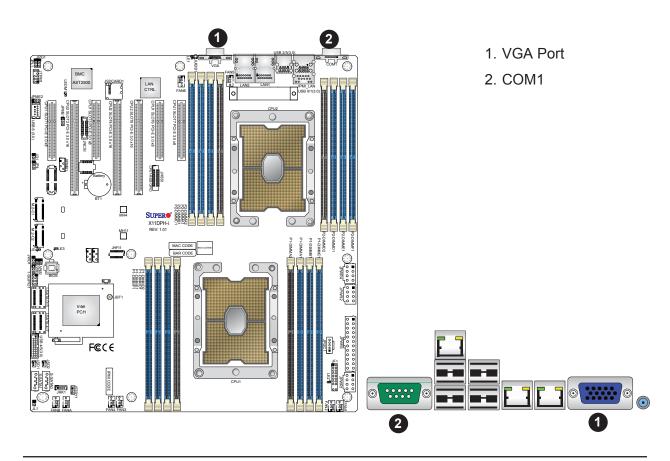

| COM1                                                             | COM port on the I/O back panel                              |                               |  |  |

| FAN1~6, FANA/FANB                                                | System/cooling fan headers                                  |                               |  |  |

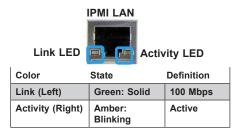

| IPMI_LAN                                                         | Dedicated IPMI LAN port                                     |                               |  |  |

| I-SATA0~3, I-SATA4~7                                             | SATA 3.0 Ports supported by the Intel PCH                   |                               |  |  |

| JD1                                                              | Speaker header                                              |                               |  |  |

| JF1                                                              | Front control panel header                                  |                               |  |  |

| JHFI1                                                            | Host Fabric Interface (HFI) sideband connection header used | for the HFI carrier card      |  |  |

| JHSSI                                                            | High-Speed Serial Interface (HSSI) card header              |                               |  |  |

| JIPMB1 4-pin External I <sup>2</sup> C Header (for an IPMI card) |                                                             |                               |  |  |

| JL1                                                              |                                                             |                               |  |  |

| JNCSI                                                            | Network Controller Sideband Interface (NCSI) header         |                               |  |  |

| JPI <sup>2</sup> C1                                              | Power I <sup>2</sup> C System Management Bus (SMBus) header |                               |  |  |

| JPWR1, JPWR2, JPWR4                                              | 8-pin power supply connectors                               |                               |  |  |

| JPWR3                                                            | 24-pin ATX main power supply connector                      |                               |  |  |

| JRK1                                                             | Intel RAID key for NVMe SDD                                 |                               |  |  |

| JSD1, JSD2                                                       | SATA DOM (Device-on-Module) power connectors                |                               |  |  |

| JSDCARD1                                                         | Micro SD card slot                                          |                               |  |  |

| JSTBY1                                                           | Standby power header                                        |                               |  |  |

| JTPM1                                                            | Trusted Platform Module (TPM)/Port 80 connector             |                               |  |  |

| JUIDB1                                                           | Unit Identifier (UID) switch                                |                               |  |  |

| LAN1, LAN2                                                       | 10GbE LAN ports (for the X11DPH-T(q)) and Gigabit LAN po    | orts (for the X11DPH-i)       |  |  |

| M.2-C1, M.2-C2                                                   | M.2 slots                                                   |                               |  |  |

| MH4, MH11                                                        | M.2 mounting holes                                          |                               |  |  |

| (CPU1) SLOT1, SLOT3,<br>SLOT6, SLOT7                             | PCI-Express 3.0 x8 Slots supported by CPU1                  |                               |  |  |

| Connector                     | Description                                |                                                 |  |  |

|-------------------------------|--------------------------------------------|-------------------------------------------------|--|--|

| (CPU2) SLOT2, SLOT4,<br>SLOT5 | PCI-Express 3.0 x16 Slot supported by CPU2 |                                                 |  |  |

| S-SATA0, S-SATA1              | Powered SATA 3.0 ports with support of     | Supermicro SuperDOM (Disk-On-Module)            |  |  |

| T-SGPIO1                      | Serial_Link General Purpose I/O (GPI/O     | )) port                                         |  |  |

| USB0/1, USB2/3                | Back Panel Universal Serial Bus (USB)      | 3.0 ports                                       |  |  |

| USB4/5                        | Internal USB 3.0 header with two USB       | (USB4/5) connections supported for front access |  |  |

| USB6                          | Type A USB 3.0 header for front access     |                                                 |  |  |

| VGA                           | VGA port                                   |                                                 |  |  |

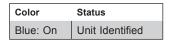

| LED                           | Description                                | Status                                          |  |  |

| LE1                           | Unit Identifier (UID) LED                  | Solid Blue: Unit Identified                     |  |  |

| LE2                           | Onboard power LED                          | Solid Green: Power On                           |  |  |

| LE3                           |                                            |                                                 |  |  |

| LE4                           |                                            |                                                 |  |  |

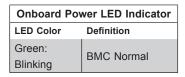

| LEDM1                         | BMC Heartbeat LED                          | Blinking Green: BMC normal                      |  |  |

### **Motherboard Features**

#### **Motherboard Features**

#### **CPU**

• Supports dual 81xx/61xx/51xx/41xx/31xx Series processors (Socket P); each processor supports an Intel® UltraPath Interconnect (UPI) of up to 10.4 GT/s. (**Note**: X11DPH-Tq supports QAT)

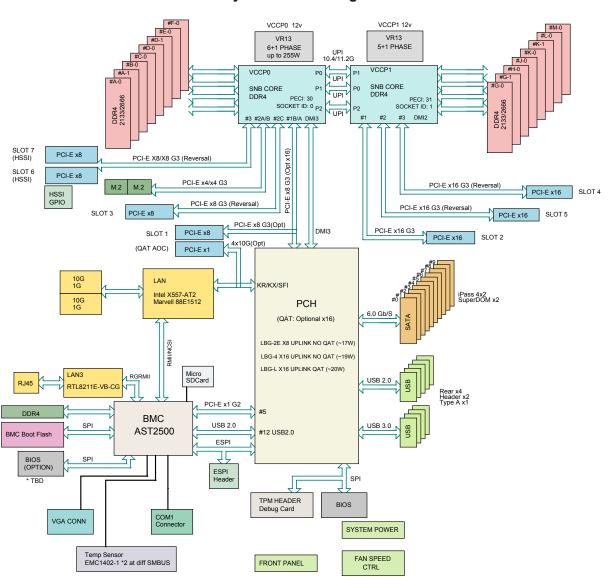

**Note:** Both CPUs need to be installed for full access to the PCI-E slots, DIMM slots, and onboard controllers. Refer to the block diagram on page 16 to determine which slots or devices may be affected.

#### Memory

• Integrated memory controller supports up to 2TB of Registered DIMM (RDIMM), Load Reduced DIMM (LRDIMM), 3D LRDIMM, Non-Volatile DIMM (NV-DIMM) DDR4 (288-pin) ECC memory with speeds of up to 2666MHz in 16 slots.

#### **DIMM Size**

• Up to 128GB at 1.2V

Note 1: Memory speed support depends on the processors used in the system.

Note 2: For the latest CPU/memory updates, please refer to our website at http://www.supermicro.com/products/motherboard.

#### Chipset

Intel C622/C624/C628 PCH (C622: is for X11DPH-i, C624 for X11DPH-T, and C628: X11DPT-Tq.)

### **Expansion Slots**

- Four (4) PCI-Express 3.0 X8 slots supported by CPU1 (SLOT1, SLOT3, SLOT6, SLOT7 3; No Slot1 for X11DPH-Tq)

- Three (3) PCI-Express 3.0 X16 slots supported by CPU2 (SLOT2, SLOT4, SLOT5)

### **Baseboard Management Controller (BMC)**

ASpeed AST2500 BMC with IPMI 2.0 support

#### **Graphics**

• Graphics controller via ASpeed AST2500 BMC

#### **Network Connection**

- Intel C628/x722 supports two 10 Gigabit LAN ports on the X11DPH-Tq

- Intel C624/x722 supports two 10 Gigabit LAN ports on the X11DPH-T

- Intel C622/x722 supports two Gigabit LAN ports (X11DPH-i)

- One (1) Dedicated IPMI LAN located on the rear I/O panel

#### I/O Devices

| Serial (COM) Port | One (1) serial port on the rear I/O panel                     |

|-------------------|---------------------------------------------------------------|

| • SATA 3.0        | • Eight (8) SATA 3.0 ports (I-SATA0~3, I-SATA4~7)             |

| - OAIA 0.0        | Two (2) SATA 3.0 ports with SATA DOM power (S-SATA0, S-SATA1) |

| • RAID (PCH)      | • RAID 0, 1, 10                                               |

#### **Motherboard Features**

### **Peripheral Devices**

- Four (4) USB 3.0 ports on the I/O back panel (USB 0/1, USB2/3)

- One (1) USB 3.0 header with two (2) USB connections for front access (USB4/5)

- One (1) USB 3.0 Type A header (USB6)

#### **BIOS**

- 64MB SPI AMI BIOS® SM Flash UEFI BIOS

- · ACPI 3.0 or later, USB keyboard, Plug-and-Play (PnP), SPI dual/quad speed support, and SMBIOS 2.7 or later

### **Power Management**

- · ACPI power management

- SuperDoctor® 5

- · Power button override mechanism

- · Wake-on LAN

- · Power-on mode for AC power recovery

- Intel® Intelligent Power Node Manager 4.0 (available when the Supermicro Power Manager [SPM] is installed and a special power supply is used

- Management Engine (ME)

#### **System Health Monitoring**

- Onboard voltage monitoring for +1.8V, +3.3V, +5V, +/-12V, +3.3V Standby, +5V Standby, VBAT, HT, memory, PCH temperature, system temperature, and memory temperature

- 6+1 CPU switch phase voltage regulator for CPU1

- 5+1 CPU switch phase voltage regulator for CPU2

- · CPU thermal trip support

- · Status monitor for speed control

- · Status monitor for on/off control

- CPU Thermal Design Power (TDP) support of up to 165W

#### **Fan Control**

- Fan status monitoring via IPMI connections

- · Eight 4-pin fan headers

- · Dual cooling zone

- · Low-noise fan speed control

- Pulse Width Modulation (PWM) fan control

#### **System Management**

- Trusted Platform Module (TPM) support

- PECI (Platform Environment Control Interface) 2.0 support

- System resource alert via SuperDoctor® 5

- SuperDoctor® 5, Watch Dog, NMI, RoHS

- · Power supply monitoring

- · Chassis intrusion header and detection

#### **Motherboard Features**

#### **LED Indicators**

- CPU/Overheating

- Power/Suspend-state indicator

- Fan failure

- UID/remote UID.

- HDD activity

- · LAN activity.

#### **Dimensions**

• 13" (W) x 12" (L) (330.2 mm x 304.8 mm)

**Note 1:** The CPU maximum thermal design power (TDP) is subject to chassis and heatsink cooling restrictions. For proper thermal management, please check the chassis and heatsink specifications for proper CPU TDP sizing.

**Note 2:** For IPMI configuration instructions, please refer to the Embedded IPMI Configuration User's Guide available at http://www.supermicro.com/support/manuals/.

**Note 3:** It is strongly recommended that you change BMC log-in information upon initial system power-on. The manufacture default username is ADMIN and the password is ADMIN. For proper BMC configuration, please refer to http://www.supermicro.com/products/info/files/IPMI/Best\_Practices\_BMC\_Security.pdf

Figure 1-3. System Block Diagram

**Note:** This is a general block diagram and may not exactly represent the features on your motherboard. See the previous pages for the actual specifications of your motherboard.

## 1.2 Processor and Chipset Overview

Built upon the functionality and capability of the Intel Xeon 81xx/61xx/51xx/41xx/31xx Series processors (Socket P) and the Intel C622/C624/C628 chipset (Note below), this motherboard provides superb system performance, efficient power management, and a rich feature set based on cutting edge technology to address the needs of next-generation computer users. With support of Intel® UltraPath Interconnect (UPI) of up to 10.4 GT/s, Intel® AVX-512 new instructions, and Intel® QuickAssist Technology, this motherboard offers an innovative solution with maximum system performance to meet the ongoing demands of High Performance Computing (HPC) platforms. This motherboard is optimized for general purpose server use. The Intel Xeon 81xx/61xx/51xx/41xx/31xx Series processor and the Intel C622/C624/C628 chipset support the following features:

- Intel® AVX-512 support with memory bandwidth increase to 6 channels (x1.5 from the previous generation)

- High availability interconnect between multiple nodes

- Rich set of available IOs, full flexibility in usage model, and software stack

- Dedicated subsystems for customer innovation

- Increased platform security with Intel® Boot Guard for hardware-based boot integrity protection; prevention of buffer overflow class security threads

- Integrated solution for real-time compression, streaming write & read performance increases from gen-to-gen

- Hot plug and enclosure management with Intel Volume Management Device (Intel VMD)

- Single standard server development (Accelerate NFV transition) consolidating application, control, and data plane workloads, reducing total platform investment needs

- Intel QuickAssist Technology off-loads compute-intensive tasks from cores

## 1.3 Special Features

This section describes the health monitoring features of the X11DPH-i/T(q) motherboard. The motherboard has an onboard ASpeed AST 2500 Baseboard Management Controller (BMC) that supports system health monitoring.

## **Recovery from AC Power Loss**

The Basic I/O System (BIOS) provides a setting that determines how the system will respond when AC power is lost and then restored to the system. You can choose for the system to remain powered off (in which case you must press the power switch to turn it back on), or for it to automatically return to the power-on state. See the Advanced BIOS Setup section for this setting. The default setting is Last State.

# 1.4 System Health Monitoring

This section describes the health monitoring features of the X11DPH-i/T(q) motherboard. The motherboard has an onboard Baseboard Management Controller (BMC) chip that supports system health monitoring. Once a voltage becomes unstable, a warning is given or an error message is sent to the screen. The user can adjust the voltage thresholds to define the sensitivity of the voltage monitor.

## **Onboard Voltage Monitors**

The onboard voltage monitor will continuously scan crucial voltage levels. Once a voltage becomes unstable, it will give a warning or send an error message to the screen. The user can adjust the voltage thresholds to define the sensitivity of the voltage monitor. Real time readings of these voltage levels are all displayed in the BIOS.

## Fan Status Monitor with Firmware Control

The system health monitor embedded in the BMC chip can check the RPM status of the cooling fans. The CPU and chassis fans are controlled via IPMI.

## **Environmental Temperature Control**

System Health sensors in the BMC monitor the temperatures and voltage settings of onboard processors and the system in real time via the IPMI interface. Whenever the temperature of the CPU or the system exceeds a user-defined threshold, system/CPU cooling fans will be turned on to prevent the CPU or the system from overheating.

$\mathbb{Q}$

**Note:** To avoid possible system overheating, please be sure to provide adequate airflow to your system.

## **System Resource Alert**

This feature is available when used with Supermicro® SuperDoctor 5. SuperDoctor 5 is used to notify the user of certain system events. For example, you can configure SuperDoctor 5 to provide you with warnings when the system temperature, CPU temperatures, voltages and fan speeds go beyond a predefined range.

## 1.5 ACPI Features

ACPI stands for Advanced Configuration and Power Interface. The ACPI specification defines a flexible and abstract hardware interface that provides a standard way to integrate power management features throughout a computer system including its hardware, operating system and application software. This enables the system to automatically turn on and off peripherals such as network cards, hard disk drives and printers.

In addition to enabling operating system-directed power management, ACPI also provides a generic system event mechanism for Plug and Play, and an operating system-independent interface for configuration control. ACPI leverages the Plug and Play BIOS data structures while providing a processor architecture-independent implementation that is compatible with Windows 10, and Windows 2012 operating systems.

# 1.6 Power Supply

As with all computer products, a stable power source is necessary for proper and reliable operation. It is even more important for processors that have high CPU clock rates. In areas where noisy power transmission is present, you may choose to install a line filter to shield the computer from noise. It is recommended that you also install a power surge protector to help avoid problems caused by power surges.

# 1.7 Super I/O

The Super I/O (ASpeed AST2500 chip) provides a high-speed, 16550 compatible serial communication port (UART), which supports serial infrared communication. The UART includes send/receive FIFO, a programmable baud rate generator, complete modem control capability, and a processor interrupt system. The UART provides legacy speed with baud rate of up to 115.2 Kbps as well as an advanced speed with baud rates of 250 K, 500 K, or 1 Mb/s, supporting higher speed modems.

The Super I/O provides functions that comply with ACPI (Advanced Configuration and Power Interface), which includes support of legacy and ACPI power management through a SMI or SCI function pin. It also features auto power management to reduce power consumption.

## 1.8 Advanced Power Management

The following new advanced power management features are supported by the motherboard.

## Intel® Intelligent Power Node Manager (IPNM)

Intel's Intelligent Power Node Manager (IPNM) provides your system with real-time thermal control and power management for maximum energy efficiency. IPNM is available when the Supermicro Power Manager (SPM) is installed. Although IPNM Specification Version 2.0 or 3.0 is supported by the BMC (Baseboard Management Controller), your system must also have IPNM-compatible Management Engine (ME) firmware installed to use this feature.

**Note:** Support for IPNM 2.0/3.0 support is dependent on the power supply used in the system.

## Management Engine (ME)

The Management Engine, which is an ARC controller embedded in the IOH (I/O Hub), provides Server Platform Services (SPS) to your system. The services provided by SPS are different from those provided by the ME on client platforms.

# 1.9 Intel® QuickAssist Technology (For the X11DPH-Tq only)

This X11DPH-T(q) supports Intel QuickAssist Technology, which provides a software-based foundation for security, authentication, and compressing, greatly enhances system performance and efficiency across applications and platforms. These improvements include symmetric encryption and authentication, asymmetric encryption, digital signatures, public key functions, compression and decompression. With Intel QAT functionality and capability built in, this motherboard is optimized for the following applications and platforms:

#### For General-Purpose Sever

This motherboard offers secure browsing, email searching, data transferring, and multitenancy.

#### For Networking

• This motherboard allows for secure routing, built-in firewalls, web proxy, WAN optimization, authentication, and 3G/4G wireless.

#### For Big Data

This motherboard offers Affinity Analytic (HADOOP).

#### For Storage

This motherboard provides real\_time data compression and secure storage.

# **Chapter 2**

## Installation

## 2.1 Static-Sensitive Devices

Electrostatic Discharge (ESD) can damage electronic components. To avoid damaging your motherboard and your system, it is important to handle it very carefully. The following measures are generally sufficient to protect your equipment from ESD.

## **Precautions**

- Use a grounded wrist strap designed to prevent static discharge.

- Touch a grounded metal object before removing the motherboard from the antistatic bag.

- Handle the motherboard by its edges only; do not touch its components, peripheral chips, memory modules or gold contacts.

- When handling chips or modules, avoid touching their pins.

- Put the motherboard and peripherals back into their antistatic bags when not in use.

- For grounding purposes, make sure that your chassis provides excellent conductivity between the power supply, the case, the mounting fasteners, and the motherboard.

- Use only the correct type of CMOS onboard battery as specified by the manufacturer. Do not install the CMOS battery upside down, which may result in a possible explosion.

## **Unpacking**

The motherboard is shipped in antistatic packaging to avoid static damage. When unpacking the motherboard, make sure that the person handling it is static protected.

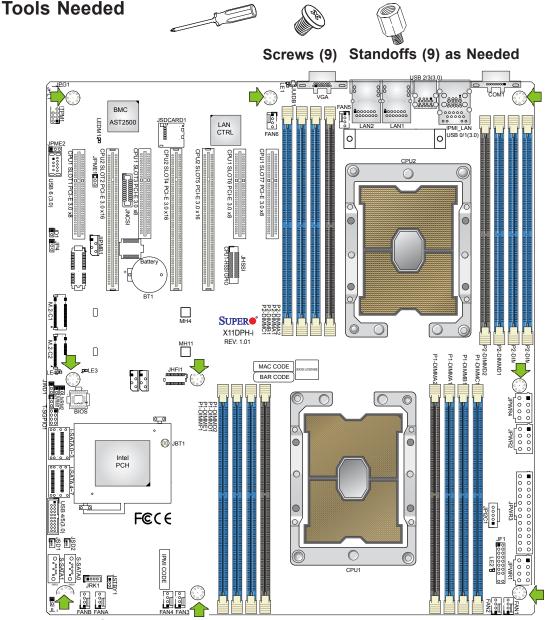

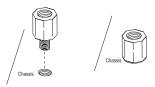

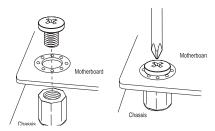

## 2.2 Motherboard Installation

All motherboards have standard mounting holes to fit different types of chassis. Make sure that the locations of all the mounting holes for both the motherboard and the chassis match. Although a chassis may have both plastic and metal mounting fasteners, metal ones are highly recommended because they ground the motherboard to the chassis. Make sure that the metal standoffs click in or are screwed in tightly.

# **Location of Mounting Holes**

**Notes:** 1) To avoid damaging the motherboard and its components, please do not use a force greater than 8 lb/inch on each mounting screw during motherboard installation. 2) Some components are very close to the mounting holes. Please take precautionary measures to avoid damaging these components when installing the motherboard to the chassis.

## Installing the Motherboard

1. Install the I/O shield into the back of the chassis.

2. Locate the mounting holes on the motherboard. See the previous page for the location.

3. Locate the matching mounting holes on the chassis. Align the mounting holes on the motherboard against the mounting holes on the chassis.

- 4. Install standoffs in the chassis as needed.

- 5. Install the motherboard into the chassis carefully to avoid damaging other motherboard components.

- 6. Using the Phillips screwdriver, insert a Pan head #6 screw into a mounting hole on the motherboard and its matching mounting hole on the chassis.

- 7. Repeat Step 5 to insert Pan head #6 screws into all mounting holes.

- 8. Make sure that the motherboard is securely placed in the chassis.

## 2.3 Processor and Heatsink Installation

**Warning:** When handling the processor package, avoid placing direct pressure on the label area of the CPU or CPU socket. Also, improper CPU installation or socket misalignment can cause serious damage to the CPU or motherboard which may result in RMA repairs. Please read and follow all instructions thoroughly before installing your CPU and heatsink.

#### Notes:

- Always connect the power cord last, and always remove it before adding, removing, or changing any hardware components. Please note that the processor and heatsink should be assembled together first to form the Processor Heatsink Module (PHM), and then install the entire PHM into the CPU socket.

- When you receive a motherboard without a processor pre-installed, make sure that the

plastic CPU socket cap is in place and that none of the socket pins are bent; otherwise,

contact your retailer immediately.

- Refer to the Supermicro website for updates on CPU support.

- Please follow the instructions given in the ESD Warning section on the first page of this chapter before handling, installing, or removing system components.

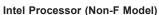

### The Intel 81xx/61xx/51xx/41xx/31xx Series Processors

**Notes:** 1. The 81xx/61xx/51xx/41xx/31xx processors contain two models: the F model processors and the Non-F model processors. The installation instructions for the F model processors differ from the installation instructions for the Non-F model processors. For this reason, two sets of instructions (one for the F model, and the other, for the Non-F model) are provided in this section. 2. If an F model CPU is used, be sure to installed in CPU Socket#1.)

Intel Processor (F Model)

**Note:** All graphics, drawings, and pictures shown in this manual are for illustration only.

The components that came with your machine may or may not look exactly the same as those shown in this manual.

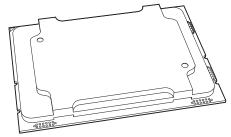

## **Overview of the Processor Socket Assembly**

The processor socket assembly contains 1) the Intel 81xx/61xx/51xx/41xx/31xx processor, 2) the narrow processor clip, 3) the dust cover, and 4) the CPU socket.

# 1. The 81xx/61xx/51xx/41xx/31xx Processor

(The 81xx/61xx/51xx/41xx/31xx Processor)

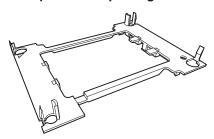

2. Narrow processor clip (the plastic processor package carrier used for the CPU)

(for the non-F Model)

3. Dust Cover

4. CPU Socket

**Note**: Be sure to cover the CPU socket with the dust cover when the CPU is not installed.

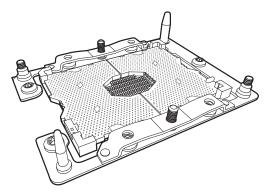

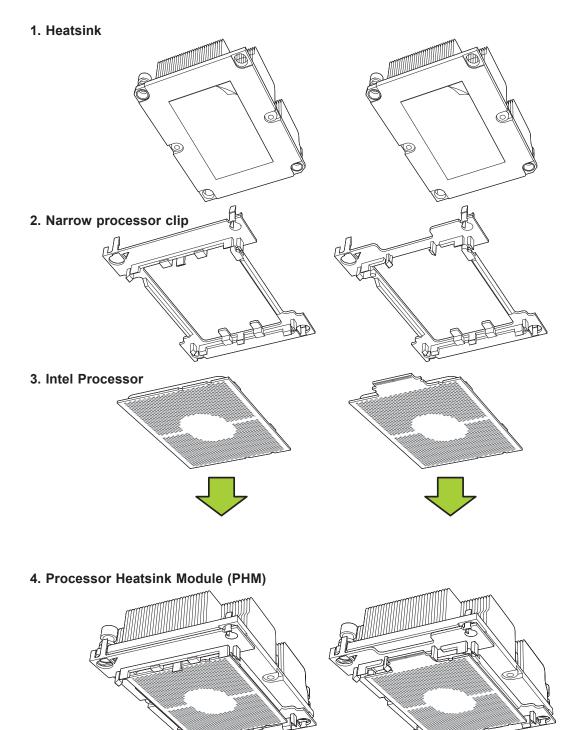

## Overview of the Processor Heatsink Module (PHM)

The Processor Heatsink Module (PHM) contains 1) a heatsink, 2) a narrow processor clip, and 3) the 81xx/61xx/51xx/41xx/31xx processor.

Processor Heatsink Module (PHM)

(Bottom View for the non-F Model) (Bottom View for the F Model)

Note: If an F model CPU is procrssor is used, be sure to install it on CPU Socket#1.

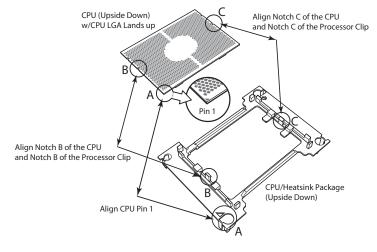

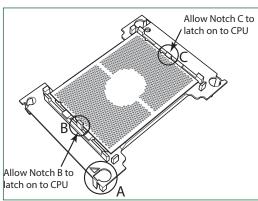

# Attaching the Non-F Model Processor to the Narrow Processor Clip to Create the Processor Package Assembly

To properly install the CPU into the narrow processor clip, please follow the steps below.

- 1. Locate pin 1 (notch A), which is the triangle located on the top of the narrow processor clip. Also locate notch B and notch C on the processor clip.

- 2. Locate pin 1 (notch A), which is the triangle on the substrate of the CPU. Also, locate notch B and notch C on the CPU as shown below.

- 3. Align pin 1 (the triangle on the substrate) of the CPU with pin 1 (the triangle) of the narrow processor clip. Once they are aligned, carefully insert the CPU into the processor clip by sliding notch B of the CPU into notch B of the processor clip, and sliding notch C of the CPU into notch C of the processor clip.

- 4. Examine all corners of the CPU to ensure that it is properly seated on the processor clip. Once the CPU is securely attached to the processor clip, the processor package assembly is created.

Note: Please exercise extreme caution when handling the CPU. Do not touch the CPU LGA-lands to avoid damaging the LGA-lands or the CPU. Be sure to wear ESD gloves when handling components.

Processor Package Carrier (w/CPU mounted on the Processor Clip)

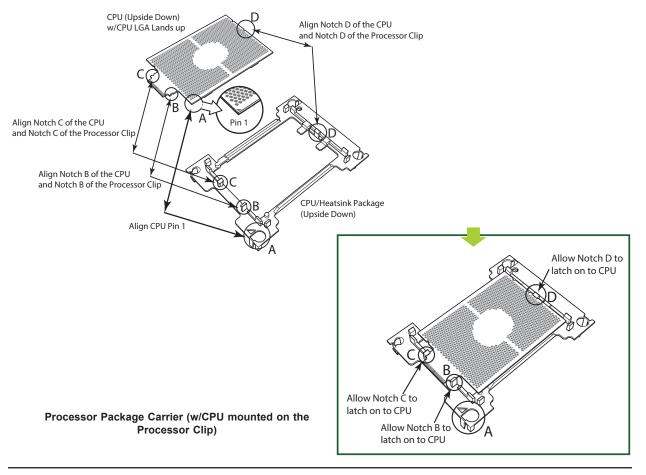

# Attaching the F Model Processor to the Narrow Processor Clip to Create the Processor Package Assembly

To properly install the CPU into the narrow processor clip, please follow the steps below.

- 1. Locate pin 1 (notch A), which is the triangle located on the top of the narrow processor clip. Also locate notch B and notch C on the processor clip.

- 2. Locate pin 1 (notch A), which is the triangle on the substrate of the CPU. Also, locate notch B and notch C on the CPU as shown below.

- 3. Align pin 1 (the triangle on the substrate) of the CPU with pin 1 (the triangle) of the narrow processor clip. Once they are aligned, carefully insert the CPU into the processor clip by sliding notch B of the CPU into notch B of the processor clip, and sliding notch C of the CPU into notch C of the processor clip.

- 4. Examine all corners of the CPU to ensure that it is properly seated on the processor clip. Once the CPU is securely attached to the processor clip, the processor package assembly is created.

**Note:** Please exercise extreme caution when handling the CPU. Do not touch the CPU LGA-lands to avoid damaging the LGA-lands or the CPU. Be sure to wear ESD gloves when handling components.

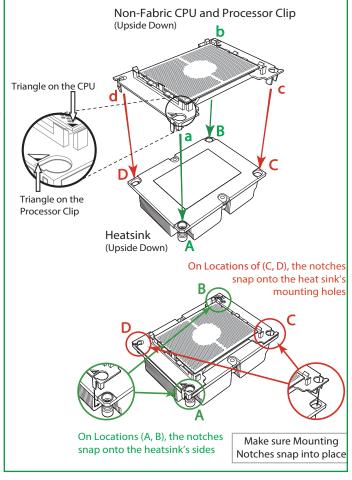

# Attaching the Non-F Model Processor Package Assembly to the Heatsink to Form the Processor Heatsink Module (PHM)

After you have made a processor package assembly by following the instructions on the previous page, please follow the steps below to mount the processor package assembly onto the heatsink to create the Processor Heatsink Module (PHM).

- 1. Locate "1" on the heatsink label and the triangular corner next to it on the heatsink. With your index finger pressing against the screw at this triangular corner, carefully hold and turn the heatsink upside down with the thermal-grease side facing up. Remove the protective thermal film if present, and apply the proper amount of the thermal grease as needed. (Skip this step if you have a new heatsink because the necessary thermal grease is pre-applied in the factory.)

- 2. Holding the processor package assembly at the center edge, turn it upside down. With the thermal-grease side facing up, locate the hollow triangle located at the corner of the processor carrier assembly ("a" in the graphic). Note a larger hole and plastic mounting clicks located next to the hollow triangle. Also locate another set of mounting clicks and a larger hole at the diagonal corner of the same (reverse) side of the

- processor carrier assembly ("b" in the graphic).3. With the back of heatsink and

- 3. With the back of heatsink and the reverse side of the processor package assembly facing up, align the triangular corner on the heatsink ("A" in the graphic) against the mounting clips next to the hollow triangle ("a") on the processor package assembly.

- Also align the triangular corner ("B") at the diagonal side of the heatsink with the corresponding clips on the processor package assembly ("b").

- 5. Once the mounting clips on the processor package assembly are properly aligned with the corresponding holes on the back of heatsink, securely attach the heatsink to the processor package assembly by snapping the mounting clips at the proper places on the heatsink to create the processor heatsink module (PHM).

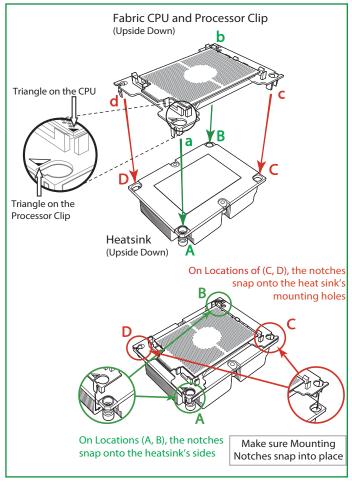

# Attaching the F Model Processor Package Assembly to the Heatsink to Form the Processor Heatsink Module (PHM)

After you have made a processor package assembly by following the instructions on the previous page, please follow the steps below to mount the processor package assembly onto the heatsink to create the Processor Heatsink Module (PHM).

- 1. Locate "1" on the heatsink label and the triangular corner next to it on the heatsink. With your index finger pressing against the screw at this triangular corner, carefully hold and turn the heatsink upside down with the thermal-grease side facing up. Remove the protective thermal film if present, and apply the proper amount of the thermal grease as needed. (Skip this step if you have a new heatsink because the necessary thermal grease is pre-applied in the factory.)

- 2. Holding the processor package assembly at the center edge, turn it upside down. With the thermal-grease side facing up, locate the hollow triangle located at the corner of the processor carrier assembly ("a" in the graphic). Note a larger hole and plastic mounting clicks located next to the hollow triangle. Also locate another set of mounting clicks and a larger hole at the diagonal corner

of the same (reverse) side of the processor carrier assembly ("b" in

the graphic).

- 3. With the back of heatsink and the reverse side of the processor package assembly facing up, align the triangular corner on the heatsink ("A" in the graphic) against the mounting clips next to the hollow triangle ("a") on the processor package assembly.

- 4. Also align the triangular corner ("B") at the diagonal side of the heatsink with the corresponding clips on the processor package assembly ("b").

- 5. Once the mounting clips on the processor package assembly are properly aligned with the corresponding holes on the back of heatsink, securely attach the heatsink to the processor package assembly by snapping the mounting clips at the proper places on the heatsink to create the processor heatsink module (PHM).

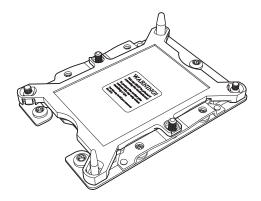

## **Preparing the CPU Socket for Installation**

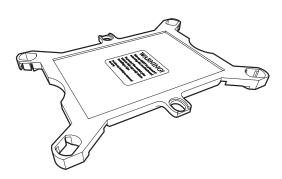

This motherboard comes with the CPU socket pre-assembled in the factory. The CPU socket contains 1) a dust cover, 2) a socket bracket, 3) the CPU (P0) socket, and 4) a back plate. These components are pre-installed on the motherboard before shipping.

CPU Socket w/Dust Cover On

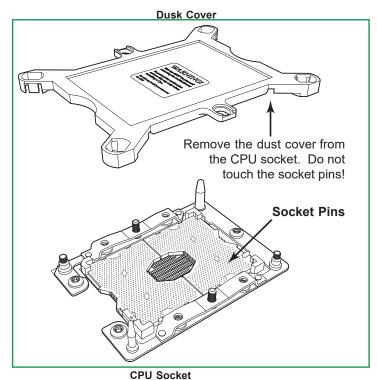

## Removing the Dust Cover from the CPU Socket

Remove the dust cover from the CPU socket, exposing the CPU socket and socket pins as shown on the illustration below.

$\mathbb{N}$

**Note**: Do not touch the socket pins to avoid damaging them, causing the CPU to malfunction.

or o oocker

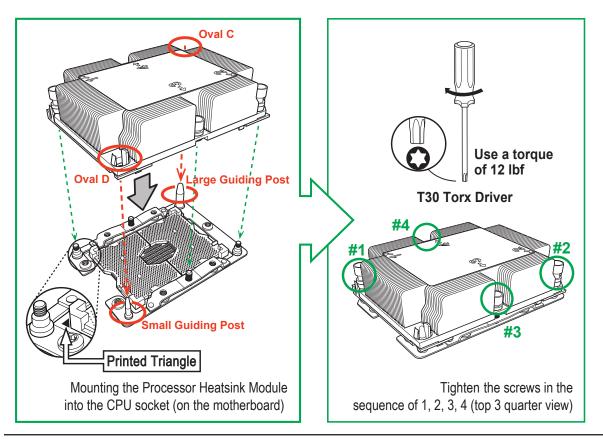

## **Installing the Processor Heatsink Module (PHM)**

- 1. Once you have assembled the processor heatsink module (PHM), you are ready to install the processor heatsink module (PHM) into the CPU socket on the motherboard. To install the PHM into the CPU socket, follow the instructions below.

- 2. Locate the triangle (pin 1) on the CPU socket, and locate the triangle (pin 1) at the corner of the PHM that is closest to "1." (If you have difficulty locating pin 1 of the PHM, turn the PHM upside down. With the LGA-lands side facing up, you will note the hollow triangle located next to a screw at the corner. Turn the PHM right side up, and you will see a triangle marked on the processor clip at the same corner of hollow triangle.)

- 3. Carefully align pin 1 (the triangle) on the the PHM against pin 1 (the triangle) on the CPU socket.

- 4. Once they are properly aligned, insert the two diagonal oval holes on the heatsink into the guiding posts.

- 5. Using a T30 Torx-bit screwdriver, install four screws into the mounting holes on the socket to securely attach the PHM onto the motherboard starting with the screw marked "1" (in the sequence of 1, 2, 3, and 4).

**Note**: Do not use excessive force when tightening the screws to avoid damaging the LGA-lands and the processor.

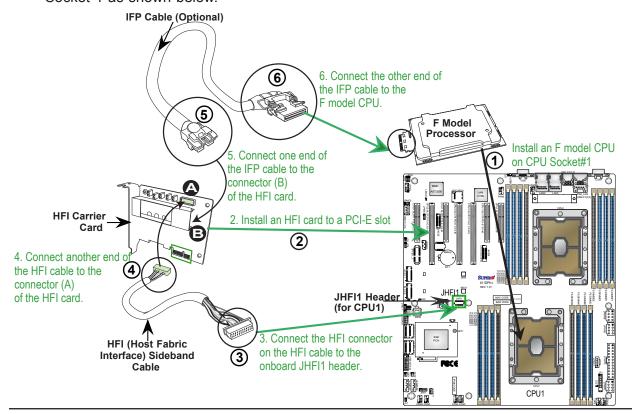

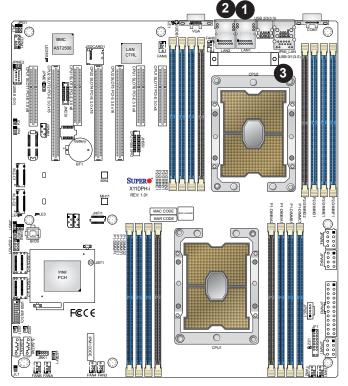

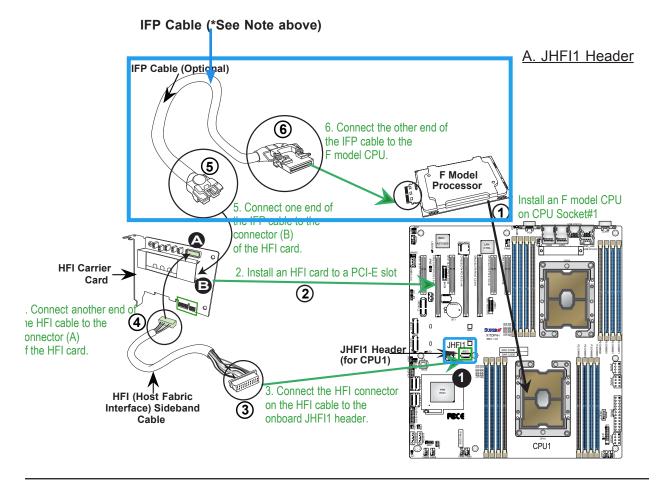

# Installing an HFI Carrier Card for Host Fabric Interface (HFI) Support as Needed (Available when an F Model CPU is Used)

**Note**: A host fabric interface carrier card header (JHFI1) is located on the motherboard. Install an HFI card on an appropriate PCI-E slot of your choice on the motherboard and an F model CPU on CPU Socket#1 to use this feature. (For more information on the JHFI1 header, please refer to page 55.)

#### Installation Instructions

- 1. Locate CPU Socket 1 on the motherboard. Install an F model CPU on this socket as shown below (marked 1) if you have not done so.

- 2. Locate the PCI-E slots the motherboard. Install an Host Fabric Interface (HFI) card on an appropriate PCI-E slot of your choice as shown below (marked 2).

- 3. Connect the HFI connector on the HFI cable to the onboard JHFI1 header as show below (marked 3 below.)

- 4. Connect the other end of the HFI cable to the connector (marked **(A)**) on the HFI card as shown below. (Marked 4 below.)

- 5. Connect the plug (marked 5) on one end of the Internal\_Faceplate\_to\_the\_Processor (IFP) cable to the connector (marked (3)) on the HFI card as shown below.

- 6. Connect the other end of IFP cable (marked 6) to the F model CPU installed in CPU Socket 1 as shown below.

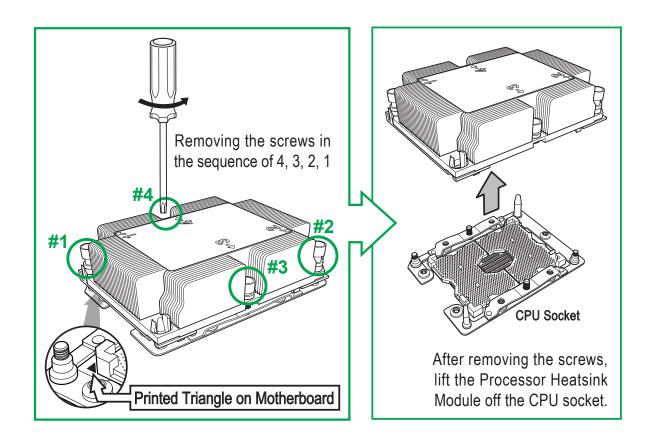

# Removing the Processor Heatsink Module (PHM) from the Motherboard

Before removing the processor heatsink module (PHM), unplug power cord from the power outlet.

- 1. Using a T30 Torx-bit screwdriver, turn the screws on the PHM counterclockwise to loosen them from the socket, starting with screw marked #4 (in the sequence of 4, 3, 2, 1).

- 2. After all four screws are removed, wiggle the PHM gently and pull it up to remove it from the socket.

**Note**: To properly remove the processor heatsink module, be sure to loosen and remove the screws on the PHM in the sequence of 4, 3, 2, 1 as shown below.

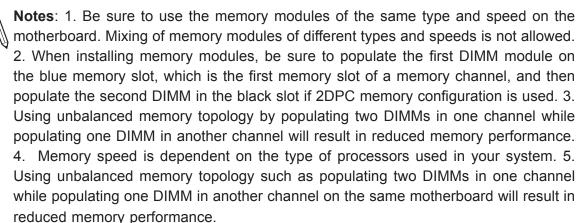

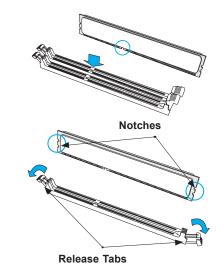

## 2.4 Memory Support and Installation

Notes: Check the Supermicro website for recommended memory modules. Exercise extreme care when installing or removing DIMM modules to prevent any damage.

## **Memory Support**

The motherboard supports up to 2TB of Registered DIMM (RDIMM), Load Reduced DIMM (LRDIMM), 3D LRDIMM, Non-Volatile DIMM (NV-DIMM) DDR4 (288-pin) ECC 2666/2400/2133 MHz memory modules in 16 slots. The black DIMM slots are reserved for future NVDIMM support. Populating the DDR4 memory module in 2DPC system configuration on this motherboard will affect memory bandwidth performance. Populating these DIMM modules with a pair of memory modules of the same type and size will result in interleaved memory, which will improve memory performance.

|             | DDR4 Memory Support (for 2-Slot Per-Channel Configuration) |                       |           |                                                                                                     |                           |  |

|-------------|------------------------------------------------------------|-----------------------|-----------|-----------------------------------------------------------------------------------------------------|---------------------------|--|

|             | Ranks<br>Per<br>DIMM<br>and Data<br>Width                  | DIMM Capacity<br>(GB) |           | Speed (MT/s); Voltage (V); Slots per Channel (SPC) and DIMMs per Channel (DPC)  2 Slots per Channel |                           |  |

| _           |                                                            |                       |           |                                                                                                     |                           |  |

| Туре        |                                                            |                       |           | 1DPC (1-DIMM per Channel)                                                                           | 2DPC (2-DIMM per Channel) |  |

|             |                                                            | 4 Gb                  | 8 Gb      | 1.2 V                                                                                               | 1.2 V                     |  |

| RDIMM       | SRx4                                                       | 8 GB                  | 16 GB     | 2666                                                                                                | 2666                      |  |

| RDIMM       | SRx8                                                       | 4 GB                  | 8 GB      | 2666                                                                                                | 2666                      |  |

| RDIMM       | DRx8                                                       | 8 GB                  | 16 GB     | 2666                                                                                                | 2666                      |  |

| RDIMM       | DRx4                                                       | 16 GB                 | 32 GB     | 2666                                                                                                | 2666                      |  |

| RDIMM 3Ds   | QRX4                                                       | N/A                   | 2H-64GB   | 2666                                                                                                | 2666                      |  |

| RDIMM 3Ds   | 8RX4                                                       | N/A                   | 4H-128GB  | 2666                                                                                                | 2666                      |  |

| LRDIMM      | QRx4                                                       | 32 GB                 | 64 GB     | 2666                                                                                                | 2666                      |  |

| L DDIMM 2D- | QRX4                                                       | N/A                   | 2H-64GB   | 2666                                                                                                | 2666                      |  |

| LRDIMM 3Ds  | 8Rx4                                                       | N/A                   | 4H-128 GB | 2666                                                                                                | 2666                      |  |

|             | DDR4 Memory Support (for 1-Slot Per-Channel Configuration) |                       |           |                                                                                |  |  |  |

|-------------|------------------------------------------------------------|-----------------------|-----------|--------------------------------------------------------------------------------|--|--|--|

|             | Ranks<br>Per<br>DIMM<br>and Data<br>Width                  | DIMM Capacity<br>(GB) |           | Speed (MT/s); Voltage (V); Slots per Channel (SPC) and DIMMs per Channel (DPC) |  |  |  |

| _           |                                                            |                       |           | 1 Slot per Channel                                                             |  |  |  |

| Type        |                                                            |                       |           | 1DPC (1-DIMM per Channel)                                                      |  |  |  |

|             |                                                            | 4 Gb                  | 8 Gb      | 1.2 V                                                                          |  |  |  |

| RDIMM       | SRx4                                                       | 8 GB                  | 16 GB     | 2666                                                                           |  |  |  |

| RDIMM       | SRx8                                                       | 4 GB                  | 8 GB      | 2666                                                                           |  |  |  |

| RDIMM       | DRx8                                                       | 8 GB                  | 16 GB     | 2666                                                                           |  |  |  |

| RDIMM       | DRx4                                                       | 16 GB                 | 32 GB     | 2666                                                                           |  |  |  |

| RDIMM 3Ds   | QRX4                                                       | N/A                   | 2H-64GB   | 2666                                                                           |  |  |  |

| RDIMM 3Ds   | 8RX4                                                       | N/A                   | 4H-128GB  | 2666                                                                           |  |  |  |

| LRDIMM      | QRx4                                                       | 32 GB                 | 64 GB     | 2666                                                                           |  |  |  |

| LRDIMM 3Ds  | QRX4                                                       | N/A                   | 2H-64GB   | 2666                                                                           |  |  |  |

| LRDIWIW 3DS | 8Rx4                                                       | N/A                   | 4H-128 GB | 2666                                                                           |  |  |  |

# DIMM Population Requirements for the 81xx/61xx/51xx/41xx/31xx Series Processors

For optimal memory performance, follow the tables below when populating memory modules.

| Key Parameters for DIMM Configurations |                                                                                                                                    |  |  |  |  |

|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Parameters                             | Possible Values                                                                                                                    |  |  |  |  |

| Number of Channels                     | 1, 2, 3, 4, 5, or 6                                                                                                                |  |  |  |  |

| Number of DIMMs per Channel            | 1DPC (1 DIMM Per Channel) or 2DPC (2 DIMMs Per Channel)                                                                            |  |  |  |  |

| DIMM Type                              | RDIMM (w/ECC), LRDIMM, 3DS-LRDIMM                                                                                                  |  |  |  |  |

| DIMM Construction                      | <ul> <li>non-3DS RDIMM Raw Cards: A/B (2RX4), C (1RX4),<br/>D (1RX8), E (2RX8)</li> <li>3DS RDIMM Raw Cards: A/B (4RX4)</li> </ul> |  |  |  |  |

|                                        | <ul> <li>non-3DS LRDIMM Raw Cards: D/E (4RX4)</li> <li>3DS LRDIMM Raw Cards: A/B (8RX4)</li> </ul>                                 |  |  |  |  |

|   | General Population Requirements                                                                            |  |  |  |  |

|---|------------------------------------------------------------------------------------------------------------|--|--|--|--|

|   | DIMM Mixing Rules                                                                                          |  |  |  |  |

| • | Please populate all memory modules with DDR4 DIMMs only.                                                   |  |  |  |  |

| • | X4 and X8 DIMMs can be mixed in the same channel.                                                          |  |  |  |  |

| • | Mixing of LRDIMMs and RDIMMs is not allowed in the same channel, across different channels, and across     |  |  |  |  |

|   | different sockets.                                                                                         |  |  |  |  |

| • | Mixing of non-3DS and 3DS LRDIMM is not allowed in the same channel, across different channels, and across |  |  |  |  |

|   | different sockets.                                                                                         |  |  |  |  |

| Mixing of DIMM Types within a Channel   |         |             |             |  |  |  |  |

|-----------------------------------------|---------|-------------|-------------|--|--|--|--|

| DIMM Types RDIMM LRDIMM 3DS LRDIMM      |         |             |             |  |  |  |  |

| RDIMM                                   | Allowed | Not Allowed | Not Allowed |  |  |  |  |

| LRDIMM                                  | Allowed | Not Allowed |             |  |  |  |  |

| 3DS LRDIMM Not Allowed NotAllowed Allow |         |             |             |  |  |  |  |

#### (DDR4 Only) Socket Level Population Requirements

DDR4 Socket Level Minimum Population Requirements

- There should be at least one DDR4 DIMM per socket.

- If only one DIMM is populated in a channel, then populate it in the slot furthest away from CPU.

- Always populate DIMMs with a higher electrical loading in DIMM0 followed by DIMM1.

|                                                                                       | (DDR4 Only) Memory Populations with Possible Mixes |                                                                         |                                                                         |                                                                           |                                                                        |  |  |  |

|---------------------------------------------------------------------------------------|----------------------------------------------------|-------------------------------------------------------------------------|-------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------|--|--|--|

| DDR4 RDIMM DIMM0/DIMM1 DIMM0/DIMM1 Config. Set A Config. Set B fig. Set C DIMM0/DIMM1 |                                                    |                                                                         |                                                                         |                                                                           |                                                                        |  |  |  |

| Within                                                                                | DDR0                                               | x8, None, x8, x8                                                        | x4, None, x4, x4                                                        | x8, x4, or x4, x8                                                         | Single Rank, None                                                      |  |  |  |

| IMC<br>DIMM<br>Popula-                                                                | DDR1                                               | None or same as DDR0                                                    | None or same as DDR0                                                    | None or same as DDR0                                                      | Single Rank, Single Rank<br>Dual Rank, Single Rank,<br>Dual Rank, None |  |  |  |

| tion                                                                                  | DDR2                                               | None or same as<br>DDR1 (excludes<br>DIMM 1 in 5DIMM<br>configurations) | None or same as<br>DDR1 (excludes<br>DIMM 1 in 5DIMM<br>configurations) | None or same as<br>DDR1 (excludes DIMM<br>1 in 5DIMM configura-<br>tions) | Dual Rank, Dual Rank,<br>Single Rank, Single Rank                      |  |  |  |

| (DDR4 Only) Memory Populations with Possible Mixes                           |      |                      |                                                      |  |

|------------------------------------------------------------------------------|------|----------------------|------------------------------------------------------|--|

| 3DS LRDIMM or 3DS RDIMM DIMM0/DIMM1 Config. Set A Possible Mixes DIMM0/DIMM1 |      |                      |                                                      |  |

| Within IMC                                                                   | DDR0 | x4, None, x4, x4     | Quad Rank, None                                      |  |

| DIMM Popu-<br>lation                                                         | DDR1 | None or same as DDR0 | Quad Rank, Quad Rank Cannot mix 3DS LRDIMM and RDIMM |  |

|                                                                              | DDR2 | None or same as DDR1 |                                                      |  |

| (DDR4 Only) Memory Populations with Possible Mixes |      |                                         |                                                                                            |  |

|----------------------------------------------------|------|-----------------------------------------|--------------------------------------------------------------------------------------------|--|

| LRDIMMS DIMM0/DIMM1 Possible Mixes DIMM0/DIMM1     |      |                                         |                                                                                            |  |

| Within IMC                                         | DDR0 | x4, None, x4, x4                        | Quad Rank, None                                                                            |  |

| DIMM Popu-<br>lation                               | DDR1 | None or same as DDR0 Note: Requirements |                                                                                            |  |

|                                                    | DDR2 | None or same as DDR1                    | *Match DIMM types installed across DDR channels within an IMC  *Always populate iMC0 first |  |

| (DDR4 Only) 2SPC Memory Configuration with x8 DIMMs |                       |                                                                                                                                                              |                 |                      |  |  |

|-----------------------------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|----------------------|--|--|

|                                                     | Total # of<br>DIMMs   | DDR Channel                                                                                                                                                  | Number of Ranks | Virtual<br>Lock Step |  |  |

| DIMM Population within an IMC                       | 1 x8 DIMM             | Must be installed on iMC0 DDR Channel 0                                                                                                                      | 1               | N/A                  |  |  |

| (Note: Uniformly                                    |                       |                                                                                                                                                              | >1              | SVLS                 |  |  |

| populate with x8<br>DRAMs DIMMs)                    | 2 x8 DIMMs            | DDR0: Populate with 1 DIMM<br>DDR1: Populate identically as DDR0                                                                                             | 1               | N/A                  |  |  |

|                                                     |                       | DDR1. Populate identically as DDR0                                                                                                                           | >1              | SVLS                 |  |  |

|                                                     | 3 x8 DIMMs            | DDR0: Populate with 1 DIMM<br>DDR1: Populate identically as DDR0                                                                                             | 1               | N/A                  |  |  |

|                                                     |                       | DDR1: Populate identically as DDR0 DDR2: Populate identically as DDR1                                                                                        | >1              | SVLS                 |  |  |

|                                                     | 4 x8 DIMMs            | DDR0: Populate with 2 DIMMs<br>DDR1: Populate identically as DDR0                                                                                            | х               | SVLS                 |  |  |

|                                                     | 5 x8 DIMMs            | DDR Channel 0, 1, 2: DIMM0 is populated with identical DIMMs, DDR Channel 0, 1: DIMM1 is populated with identical DIMMs                                      | >1              | SVLS                 |  |  |

|                                                     | 6 x8 DIMMs            | Populate 2 DIMMs per DDR channel                                                                                                                             | х               | SVLS                 |  |  |

| DIMM Population                                     | 1 pair of             | DDR0: Populate with 1 DIMM                                                                                                                                   | 1               | N/A                  |  |  |

| within an IMC<br>(Note: Non-equal                   | DIMMs                 | DDR1: Populate the second DIMM (for best performance)                                                                                                        | >1              | SVLS                 |  |  |

| in rank pair of x8<br>DIMMs)                        | 2 pairs of            | DDR0: Populate with 1 pair of non-equal rank DIMMs                                                                                                           | 1               | N/A                  |  |  |

|                                                     | DIMMs                 | DDR1: Populate identically as DDR0                                                                                                                           | >1              | SVLS                 |  |  |

|                                                     | 3 pairs of DIMMs      | DDR0: Populate with 1 pair of non-equal rank DIMMs<br>DDR1: Populate identically as DDR0<br>DDR2: Populate identically as DDR1                               | х               | SVLS                 |  |  |

|                                                     | 2 pairs+1<br>(5DIMMs) | DDR0: Populate with 1 pair of non-equal rank DIMMs<br>DDR1: Populate with identical DIMMs as DDR0<br>DDR2: DIMM0 is populated with identical DIMM as<br>DDR1 | >1              | SVLS                 |  |  |

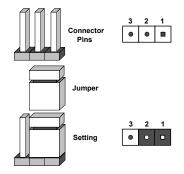

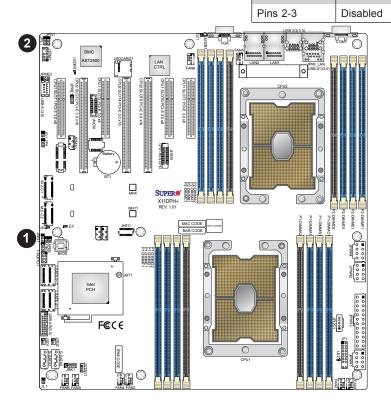

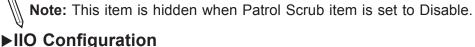

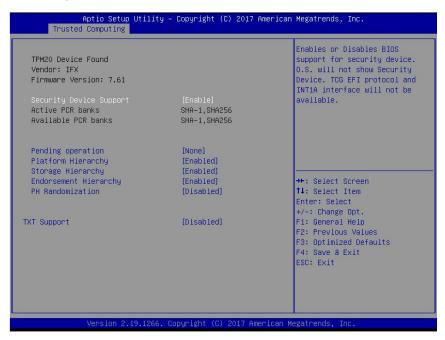

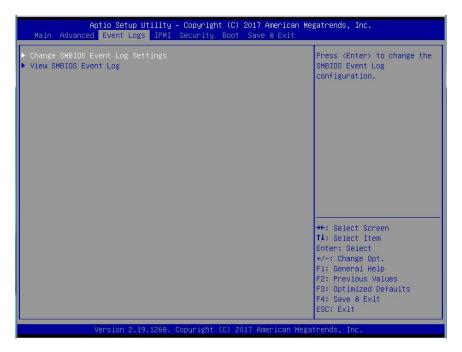

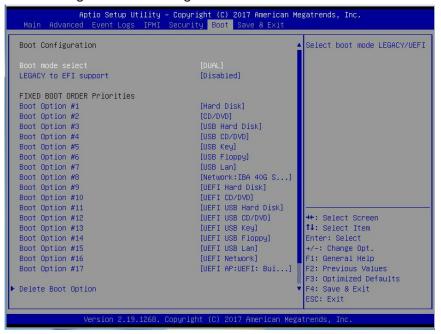

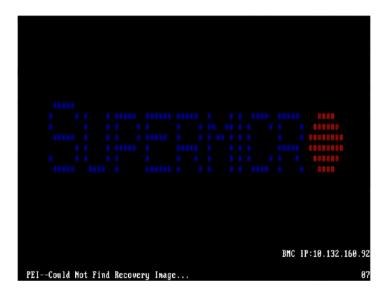

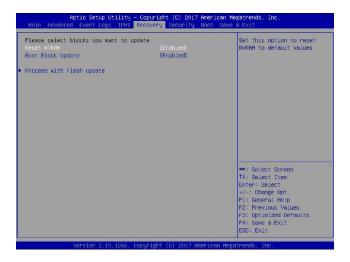

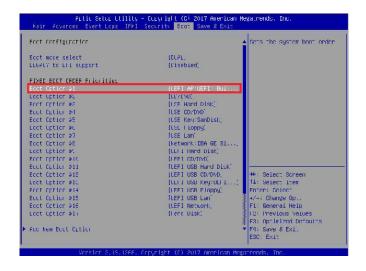

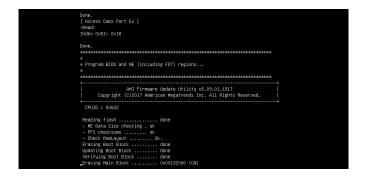

|                                                     | (DDR4 Only) 2SPC Memory Configuration with x4 DIMMs |                                                                                                                                                              |                 |                               |  |  |  |